IA32 Manual Conventions: Difference between revisions

TheCatgirls (talk | contribs) (Initial description of some IA32 manual conventions) |

TheCatgirls (talk | contribs) m (Add to x86 category) |

||

| Line 12: | Line 12: | ||

</pre> | </pre> | ||

Puts [[Segment Selector]] with [[Requested Priviledge Level|RPL]]=0 into the ''second'' (2, 0b10, 0x2) entry of the ''[[Global Descriptor Table|GDT]]'', with the 1 being the 4th bit aka bit 3 into the [[Code Segment Register|CS register]]. | Puts [[Segment Selector]] with [[Requested Priviledge Level|RPL]]=0 into the ''second'' (2, 0b10, 0x2) entry of the ''[[Global Descriptor Table|GDT]]'', with the 1 being the 4th bit aka bit 3 into the [[Code Segment Register|CS register]]. | ||

[[Category:X86]] | |||

Latest revision as of 15:09, 19 December 2024

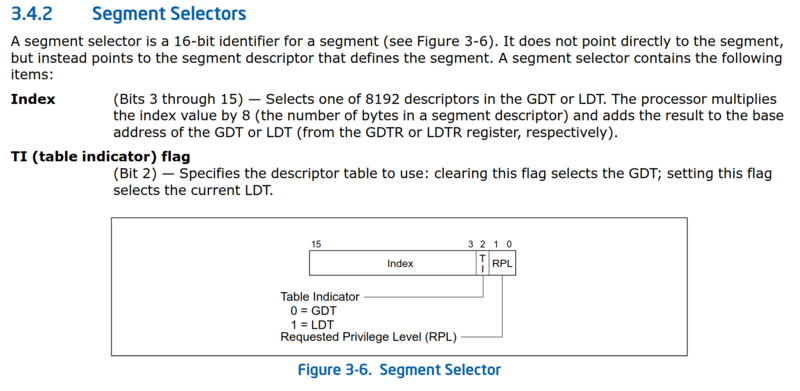

Bit number 0 is the first, Least Significant Bit. Bit ranges are written inclusive. Example with Segment Selectors:

Bit 0 is the least significant bit, bit 15 is the Most Significant Bit. Range "bits 3 through 15" include bit 3 and bit 15 and are 13 bits long, with bit 0 through 1 aka bit 0 and 1 being the RPL and bit 2 (3rd bit) being the TI.

Additionally, in memory, this is stored Little Endian, so the least significant half of the index + 3 bits for the flags is in the first byte and the most significant half of the index is in the second byte.

Do note that eg. NASM treats 0b as numeric literals, so it'll swap the bytes around - Thus,

mov ax, 0000_0000_0000_1000b mov cs, ax

Puts Segment Selector with RPL=0 into the second (2, 0b10, 0x2) entry of the GDT, with the 1 being the 4th bit aka bit 3 into the CS register.